# Sirius OBC and TCM User Manual Rev. G

#### © ÅAC Microtec 2017

ÅAC Microtec AB owns the copyright of this document which is supplied in confidence and which shall not be used for any purpose other than for which it is supplied and shall not in whole or in part be reproduced, copied, or communicated to any person without written permission from the owner.

Document number Version Issue date 205065 Rev. G 2017-10-31

Sirius OBC and TCM User Manual

www.aacmicrotec.com Page 2 of 156

# **REVISION LOG**

| Rev | Date       | Change description                                                                                                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α   | 2016-10-25 | First release, drafted from 204911 Sirius Breadboard User Manual Rev L                                                                                                                                                                                                                                                                                       |

| В   | 2016-12-15 | Updated after editorial updates Release with updates to the following sections:  • Massmem (new API with DMA)  • Error manager (IOCTL API)  • ADC (channel table update, channel limitation)  • Sirius TCM (TM/TC defaults, API updates {errno, MMStatus, TMTSStatus, }, removed limitations)  • Bootrom (extended description)                              |

| D   | 2017-02-01 | <ul> <li>SCET (extended description, new API)</li> <li>UART32 (removed)</li> <li>CCSDS (interrupt API deprecation)</li> <li>NVRAM (EDAC/non-EDAC modes described)</li> <li>Release with updates to the following sections:</li> <li>Sirius TCM (Extra info sections, TMBRSet-&gt;TMBRControl)</li> <li>Mass memory (IOCTL API, error inject info)</li> </ul> |

| E   | 2017-03-01 | SCET (Clarify threshold)  Release with updates to the following sections:     ADC (minor updates to clock div limits)     Setup and operation (find debugger serial, use of multiple debuggers)                                                                                                                                                              |

| F   | 2017-04-18 | <ul> <li>Release with updates to the following sections:</li> <li>CCSDS (new API)</li> <li>Sirius TCM (new timesync API, NVRAM table updated, new segment sizing for partitions)</li> </ul>                                                                                                                                                                  |

| G   | 2017-10-31 | <ul> <li>Release with updates to the following sections:</li> <li>Fault tolerant design (new section)</li> <li>CCSDS (updated API)</li> <li>Mass memory (updated API)</li> <li>Sirius TCM (new mass memory partition configuration behaviour &amp; RMAP API)</li> <li>System flash (new)</li> </ul>                                                          |

## **TABLE OF CONTENT**

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1. Applicable releases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8        |

| 1.2. Intended users                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8        |

| 1.3. Getting support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8        |

| 1.4. Reference documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2. EQUIPMENT INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10       |

| 2.1. System Overview with peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10       |

| 2.2. Fault tolerant design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11       |

| 3. SETUP AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13       |

| 3.1. User prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13       |

| 3.2. Connecting cables to the Sirius products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 3.3. Installation of toolchain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 3.3.1. Supported Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 3.3.2. Installation Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 3.4. Installing the Board Support Package (BSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16       |

| 3.5. Deploying a Sirius application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17       |

| 3.5.1. Establish a debugger connection to the Sirius products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17       |

| 3.5.2. Setup a serial terminal to the device debug UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17       |

| 3.5.3. Loading an application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 3.5.4. Using multiple debuggers on the same PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 3.5.4. Using multiple debuggers on the same PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 3.6. Programming an application (boot image) to system flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19       |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20       |

| SOFTWARE DEVELOPMENT  4. RTEMS step-by-step compilation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>20 |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20<br>20 |

| 4. SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>   |

| 4. SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 4. SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 3.6. Programming an application (boot image) to system flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog  5.2.1. Description  5.2.2. RTEMS API                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 3.6. Programming an application (boot image) to system flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog  5.2.1. Description  5.2.2. RTEMS API  5.2.3. Usage  5.3. Error Manager                                                                                                                                                                                                                                                                                                                                                   |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog  5.2.1. Description  5.2.2. RTEMS API  5.2.3. Usage  5.3. Error Manager  5.3.1. Description                                                                                                                                                                                                                                                                                                                               |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog  5.2.1. Description  5.2.2. RTEMS API  5.2.3. Usage  5.3. Error Manager  5.3.1. Description  5.3.2. RTEMS API                                                                                                                                                                                                                                                                                                             |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation  4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction  5.2. Watchdog  5.2.1. Description  5.2.2. RTEMS API  5.2.3. Usage  5.3. Error Manager  5.3.1. Description  5.3.2. RTEMS API  5.3.3. Usage                                                                                                                                                                                                                                                                                               |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation.  4.2. Software disclaimer of warranty  5. RTEMS.  5.1. Introduction  5.2. Watchdog.  5.2.1. Description  5.2.2. RTEMS API.  5.3.3. Usage.  5.3.1. Description  5.3.2. RTEMS API.  5.3.3. Usage.  5.3.4. Limitations.                                                                                                                                                                                                                                                                                       |          |

| 3.6. Programming an application (boot image) to system flash 4. SOFTWARE DEVELOPMENT 4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS 5.1. Introduction 5.2. Watchdog 5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage 5.3. Error Manager 5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations 5.4. SCET                                                                                                                                                                                                                                                                              |          |

| 3.6. Programming an application (boot image) to system flash 4. SOFTWARE DEVELOPMENT 4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS 5.1. Introduction 5.2. Watchdog 5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage. 5.3. Error Manager 5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations. 5.4. SCET 5.4.1. Description                                                                                                                                                                                                                                                         |          |

| 3.6. Programming an application (boot image) to system flash 4. SOFTWARE DEVELOPMENT 4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS 5.1. Introduction 5.2. Watchdog 5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage 5.3. Error Manager 5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations 5.4. SCET 5.4.1. Description 5.4.2. General purpose triggers                                                                                                                                                                                                                           |          |

| 3.6. Programming an application (boot image) to system flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT 4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS 5.1. Introduction 5.2. Watchdog 5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage 5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations 5.4. SCET 5.4.1. Description 5.4.2. General purpose triggers 5.4.3. Pulse-Per-Second (PPS) signals 5.4.4. RTEMS API 5.4.5.5.4. |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT  4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS  5.1. Introduction 5.2. Watchdog  5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage  5.3. Error Manager  5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations  5.4. SCET  5.4.1. Description 5.4.2. General purpose triggers 5.4.3. Pulse-Per-Second (PPS) signals 5.4.4. RTEMS API 5.4.5. Usage                                                                                                                                               |          |

| 3.6. Programming an application (boot image) to system flash  4. SOFTWARE DEVELOPMENT 4.1. RTEMS step-by-step compilation 4.2. Software disclaimer of warranty  5. RTEMS 5.1. Introduction 5.2. Watchdog 5.2.1. Description 5.2.2. RTEMS API 5.2.3. Usage 5.3.1. Description 5.3.2. RTEMS API 5.3.3. Usage 5.3.4. Limitations 5.4. SCET 5.4.1. Description 5.4.2. General purpose triggers 5.4.3. Pulse-Per-Second (PPS) signals 5.4.4. RTEMS API 5.4.5.5.4. |          |

| 5.4.8. RTEMS application example               | 41  |

|------------------------------------------------|-----|

| 5.5. UART                                      | 44  |

| 5.5.1. Description                             | 44  |

| 5.5.2. RTEMS API                               | 44  |

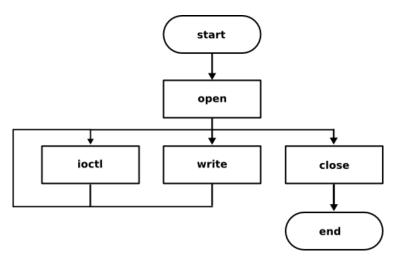

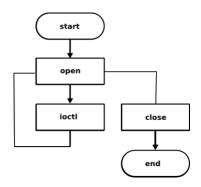

| 5.5.3. Usage description                       | 48  |

| 5.5.4. Limitations                             | 48  |

| 5.6. Mass memory                               | 49  |

| 5.6.1. Description                             | 49  |

| 5.6.2. Data Structures                         | 49  |

| 5.6.3. RTEMS API                               |     |

| 5.6.4. Usage                                   |     |

| 5.6.5. Error injection                         | 61  |

| 5.6.6. Limitations                             | 61  |

| 5.7. Spacewire                                 |     |

| 5.7.1. Description                             |     |

| 5.7.2. RTEMS API                               |     |

| 5.7.3. Usage description                       |     |

| 5.8. GPIO                                      |     |

| 5.8.1. Description                             |     |

| 5.8.2. RTEMS API                               |     |

| 5.8.3. Usage description                       |     |

| 5.8.4. Limitations                             |     |

| 5.9. CCSDS                                     |     |

| 5.9.1. Description                             |     |

| 5.9.2. Non-blocking                            |     |

| 5.9.3. Blocking                                |     |

| 5.9.4. Buffer data containing TM Space packets |     |

| 5.9.5. RTEMS API                               |     |

| 5.9.6. Usage description                       |     |

| 5.10. ADC                                      |     |

| 5.10.1. Description                            |     |

| 5.10.2. RTEMS API                              |     |

| 5.10.3. Usage description                      |     |

| 5.10.4. Limitations                            |     |

| 5.11. NVRAM                                    |     |

| 5.11.1. Description                            |     |

| 5.11.2. EDAC mode                              |     |

| 5.11.3. Non-EDAC mode                          |     |

| 5.11.4. RTEMS API                              |     |

| 5.11.5. Usage description                      |     |

| 5.12. System flash                             |     |

| 5.12.1. Description                            | 94  |

| 5.12.2. Data structure types                   |     |

| 5.12.3. RTEMS API                              |     |

| 5.12.4. Usage description                      |     |

| 5.12.5. Debug detect                           |     |

| 5.12.6. Limitations                            | 102 |

| 6. SPACEWIRE ROUTER                            | 103 |

| 7. SIRIUS TCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

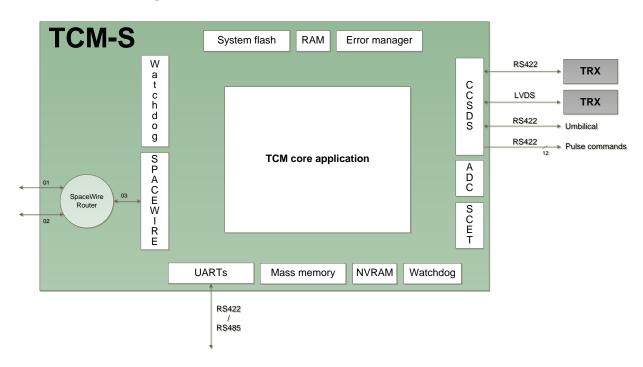

| 7.1. Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104                                                         |

| 7.2. Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 105                                                         |

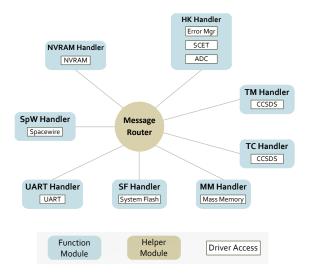

| 7.3. TCM-S application overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105                                                         |

| 7.4. Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106                                                         |

| 7.5. Telemetry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109                                                         |

| 7.6. Telecommands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 109                                                         |

| 7.6.1. Pulse commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110                                                         |

| 7.6.2. COP-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110                                                         |

| 7.7. Time Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

| 7.7.1. TM time stamps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| 7.8. Error Management and System Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111                                                         |

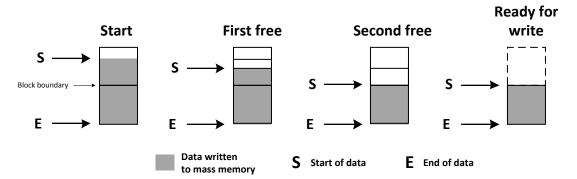

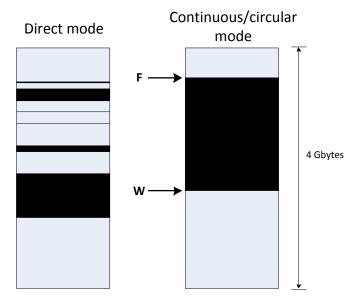

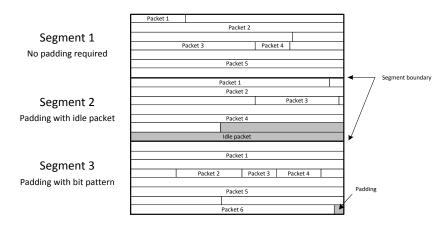

| 7.9. Mass Memory Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 7.9.1. Partition configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 7.9.2. Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 114                                                         |

| 7.10. ECSS standard services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115                                                         |

| 7.10.1. PUS-1 Telecommand verification service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115                                                         |

| 7.10.2. PUS-2 Device Command Distribution Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 115                                                         |

| 7.11. Spacewire RMAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

| 7.11.1. Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117                                                         |

| 7.11.2. Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 7.11.3. Status code in reply messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| 7.11.4. RMAP input address details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

| 7.11.5. RMAP output address details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

| 7.12. Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 136                                                         |

| 8. SYSTEM-ON-CHIP DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

| 8. SYSTEM-ON-CHIP DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 136                                                         |

| 8. SYSTEM-ON-CHIP DEFINITIONS  8.1. Memory mapping  8.2. Interrupt sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 136<br>137                                                  |

| 8. SYSTEM-ON-CHIP DEFINITIONS  8.1. Memory mapping  8.2. Interrupt sources  8.3. SCET timestamp trigger sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 136<br>137<br>137                                           |

| 8. SYSTEM-ON-CHIP DEFINITIONS  8.1. Memory mapping  8.2. Interrupt sources  8.3. SCET timestamp trigger sources  8.4. Boot images and boot procedure                                                                                                                                                                                                                                                                                                                                                                                                                                   | 136<br>137<br>137<br>138                                    |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 136<br>137<br>138<br>138                                    |

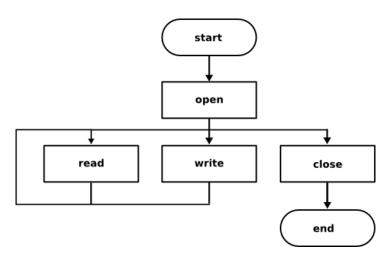

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram                                                                                                                                                                                                                                                                                                                                                                                               | 136<br>137<br>138<br>138<br>138                             |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 136<br>137<br>137<br>138<br>138<br>138                      |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations                                                                                                                                                                                                                                                                                                                                                   | 136<br>137<br>138<br>138<br>138<br>138<br>139               |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour                                                                                                                                                                                                                                                                                                                              | 136<br>137<br>138<br>138<br>138<br>139<br>139               |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method                                                                                                                                                                                                                                                                                              | 136 137 138 138 138 138 139 139                             |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs                                                                                                                                                                                                                                                                    | 136 137 138 138 138 139 139 139                             |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method                                                                                                                                                                                                                                                                                              | 136 137 138 138 138 139 139 139                             |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 136 137 138 138 138 139 139 139 139                         |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map 9. CONNECTOR INTERFACES                                                                                                                                                                                                                   | 136 137 138 138 138 139 139 139 140                         |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector                                                                                                                                                                               | 136 137 138 138 138 139 139 139 140 141                     |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW                                                                                                                                                                 | 136 137 138 138 138 139 139 139 140 141                     |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW 9.3. PWR – Power                                                                                                                                                | 136 137 138 138 138 139 139 139 140 141 141                 |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW 9.3. PWR – Power 9.4. SPW1 – Spacewire 1                                                                                                                        | 136 137 138 138 138 139 139 139 140 141 141 142 142         |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW 9.3. PWR – Power 9.4. SPW1 – Spacewire 1                                                                                                                        | 136 137 138 138 138 139 139 139 140 141 141 141 142 142     |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW 9.3. PWR - Power 9.4. SPW1 - Spacewire 1 9.5. SPW2 - Spacewire 2 9.6. ANALOG, Analog input and 3xGPIO (Sirius OBC only)                                         | 136 137 138 138 138 139 139 140 141 141 141 142 143         |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure. 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW. 9.3. PWR - Power 9.4. SPW1 - Spacewire 1. 9.5. SPW2 - Spacewire 2. 9.6. ANALOG, Analog input and 3xGPIO (Sirius OBC only) 9.7. DIGITAL, PPS input and 12xGPIO | 136137138138138139139140141141141142142143143               |

| 8. SYSTEM-ON-CHIP DEFINITIONS 8.1. Memory mapping 8.2. Interrupt sources 8.3. SCET timestamp trigger sources 8.4. Boot images and boot procedure 8.4.1. Description 8.4.2. Block diagram 8.4.3. Usage description 8.4.4. Limitations 8.5. Reset behaviour 8.6. General synchronize method 8.7. Pulse command inputs 8.8. SoC information map  9. CONNECTOR INTERFACES 9.1. JTAG-RTL, FPGA-JTAG connector 9.2. DEBUG-SW 9.3. PWR - Power 9.4. SPW1 - Spacewire 1 9.5. SPW2 - Spacewire 2 9.6. ANALOG, Analog input and 3xGPIO (Sirius OBC only)                                         | 136 137 138 138 138 139 139 140 141 141 142 142 143 143 144 |

| 9.10. TRX1 - RS422 Transceiver interface (Sirius TCM only) | 147 |

|------------------------------------------------------------|-----|

| 9.11. TRX2 - LVDS Transceiver interface (Sirius TCM only)  | 147 |

| 9.12. UMBI – Baseband Umbilical (Sirius TCM only)          | 148 |

| 9.13. Pulse Command Outputs (Sirius TCM only)              | 149 |

| 10. UPDATING THE SIRIUS FPGA                               | 150 |

| 10.1. Prerequisite hardware                                | 150 |

| 10.2. Prerequisite software                                | 150 |

| 10.3. Step by step guide                                   | 150 |

| 11. MECHANICAL DATA                                        | 153 |

| 12 GLOSSARY                                                | 154 |

# 1. Introduction

This manual describes the functionality and usage of the ÅAC Sirius OBC and Sirius TCM products. The Sirius OBC or Sirius TCM differ in certain areas such as the SoC, interfaces etc. but can mostly be described with the same functionality and will throughout this document be referred to as "the Sirius products" when both products are referred at the same time.

# 1.1. Applicable releases

This version of the manual is applicable to the following software releases:

Sirius OBC 1.0.0 Sirius TCM 1.0.0

## 1.2. Intended users

This manual is written for software engineers using the ÅAC Sirius products. The electrical and mechanical interface is described in more detail in the electrical and mechanical ICD documents [RD10] and [RD11].

## 1.3. Getting support

If you encounter any problem using the Sirius products or another ÅAC product please use the following address to get help:

Email: support@aacmicrotec.com

## 1.4. Reference documents

| RD#  | Document ref                               | Document name                                                                                   |

|------|--------------------------------------------|-------------------------------------------------------------------------------------------------|

| RD1  | http://opencores.org/openrisc,architecture | OpenRISC 1000 Architecture<br>Manual                                                            |

| RD2  | ECSS-E-ST-50-12C                           | SpaceWire – Links, nodes, routers and networks                                                  |

| RD3  | ECSS-E-ST-50-52C                           | SpaceWire – Remote memory access protocol                                                       |

| RD4  | ECSS-E-70-41A                              | Ground systems and operations – Telemetry and telecommand packet utilization PC16550D Universal |

| RD5  | SNLS378B                                   | Asynchronous<br>Receiver/Transmitter with<br>FIFOs                                              |

| RD6  | AD7173-8, Rev. A                           | Low Power, 8-/16-Channel,<br>31.25 kSPS, 24-Bit, Highly<br>Integrated Sigma-Delta ADC           |

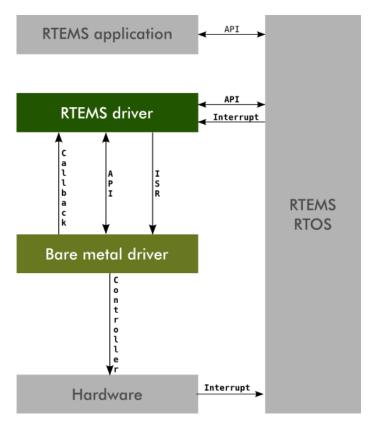

| RD7  | Edition 4.10.99.0                          | RTEMS BSP and Device Driver Development Guide                                                   |

| RD8  | CCSDS 132.0-B-2                            | TM Space Data Link Protocol                                                                     |

| RD9  | CCSDS 232.0-B-2                            | TC Space Data Link Protocol                                                                     |

| RD10 | P2-2-96-ICD-014                            | Sirius OBC electrical and mechanical ICD                                                        |

| RD11 | P2-2-96-ICD-013                            | Sirius TCM electrical and mechanical ICD Electrostatics - Part 5-1:                             |

| RD12 | SS-EN 61340-5-1                            | Protection of electronic devices from electrostatic phenomena - General requirements            |

# 2. Equipment information

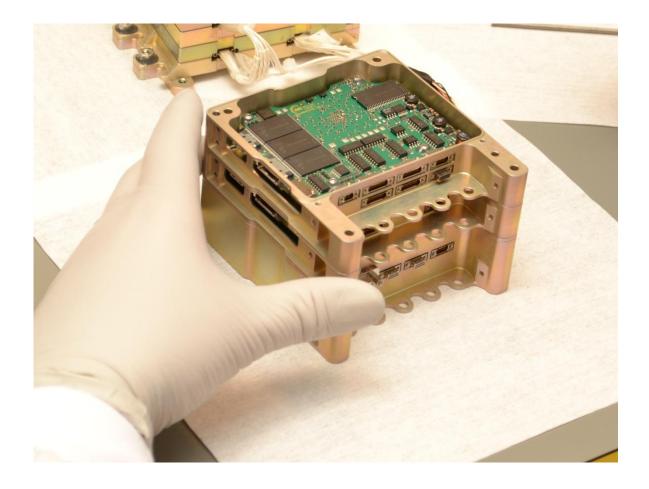

The Sirius OBC and Sirius TCM products are depicted in Figure 3-1 and Figure 3-2.

The Sirius products also include both a debugger interface for downloading and debugging software applications and a JTAG interface for programming the FPGA during manufacturing.

The FPGA firmware implements a SoC centered around a 32 bit OpenRISC Fault Tolerant processor [RD1] running at a system frequency of 50 MHz and with the following set of peripherals:

- Error manager, error handling, tracking and log of e.g. power loss and/or memory error detection.

- SDRAM 64 MB data + 64 MB EDAC running @100MHz

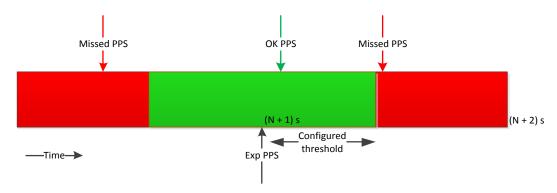

- Spacecraft Elapsed Timer (SCET), including a PPS (Pulse Per Second) time synchronization interface for accurate time measurement with a resolution of 15  $\mu$ s

- SpaceWire, including a three-port SpaceWire router, for communication with external peripheral units

- UARTs uses the RS422 and RS485 line drivers on the board with line driver mode set by software.

- GPIOs

- Watchdog, a fail-safe mechanism to prevent a system lockup

- System flash of 2 GB with EDAC-protection for storing boot images in multiple copies

- Pulse command inputs for reset to a specific software image

- NVRAM for storage of metadata and other data that requires a large number of writes that shall survive loss of power

For the Sirius TCM the following additional peripherals are included in the SoC:

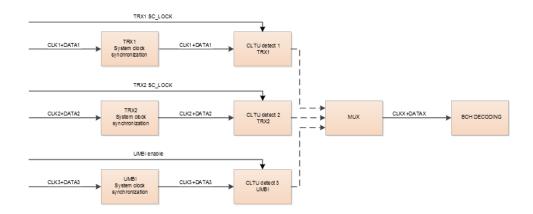

- CCSDS, communications IP with RS422/LVDS interfaces for radio communication and a UMBI interface for communication with EGSE

- Mass memory of 16GB with EDAC-protection, NAND flash based, for storage of mission critical data.

For the Sirius OBC an Analog interface is included for internal house-keeping and external analog measurements.

The input power supply provided to the Sirius products shall be between +4.5 and +16 VDC. The power consumption is highly dependent on peripheral loads and ranges from 0.8 W to 2 W.

# 2.1. System Overview with peripherals

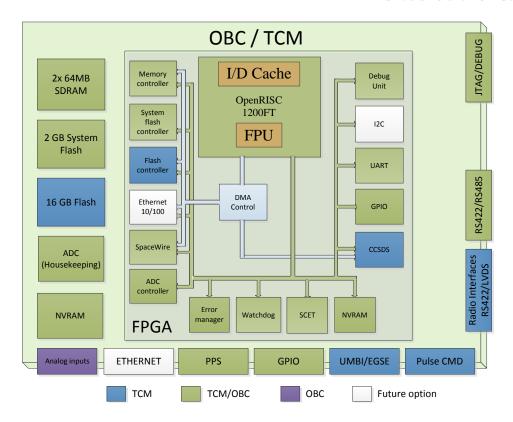

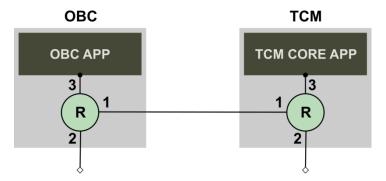

Figure 2-1 depicts a System-on-Chip (SoC) overview including the related peripherals of the Sirius OBC and Sirius TCM products. The figure shows what parts that are included for which products.

Figure 2-1 - The Sirius OBC / Sirius TCM SoC Overview

# 2.2. Fault tolerant design

The Sirius OBC and Sirius TCM are both fault tolerant by design to withstand the environmental loads that the modules are subjected to when used in space applications. The following error mitigation techniques are used.

- Continuous EDAC scrubbing of SDRAM data with at least 1 bit error correction and 2 bit error detection. Non-correctable errors cause processor interrupt to allow the software to handle the error differently depending on in which section of the memory it appeared.

- EDAC checking of instructions before execution (at least 1 bit error correction and 2 bit error detection as described in the previous point). Non-correctable errors cause automatic reboot.

- Parity checking of Instruction and Data caches in designs which include caches.

Errors cause cache reload.

- Parity checking of peripheral FIFOs. Errors cause processor interrupt.

- EDAC checking on system flash with double bit error correction and extended bit error detection in combination with interleaving that corrects bursts with up to 16bits in error.

- Power loss detection and power buffer for critical parameter storage to NVRAM.

- Triple Modular Redundancy (TMR) on all FPGA flip-flops

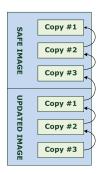

- All software stored in boot flash is protected through ECC encoding and boot images are doubled to allow for an automatic fallback option if the ECC check fails on one image.

- FPGA SEU bank lock-up detection. Bank SEU leads to automatic reboot of the device.

- Watchdog, tripping leads to automatic reboot of the device.

- Advanced Error Manager keeping the detected failures during reset/reboot for later analysis.

# 3. Setup and operation

## 3.1. User prerequisites

The following hardware and software is needed for the setup and operation of the Sirius products.

## **PC** computer

- 1 GB free space for installation (minimum)

- Debian 7 or 8 64-bit with super user rights

- USB 2.0

#### JTAG debugger

ÅAC JTAG debugger hardware including harness

#### Recommended applications and software

- Installed serial communication terminal, e.g. gtkterm or minicom

- · Host build system, e.g. the debian package build-essential

- The following software is installed by the ÅAC toolchain package

- o GCC, C compiler for OpenRISC

- o GCC, C++ compiler for OpenRISC

- GNU binutils and linker for OpenRISC

- o Custom openocd binary designed for OpenRISC

#### For FPGA update capabilities

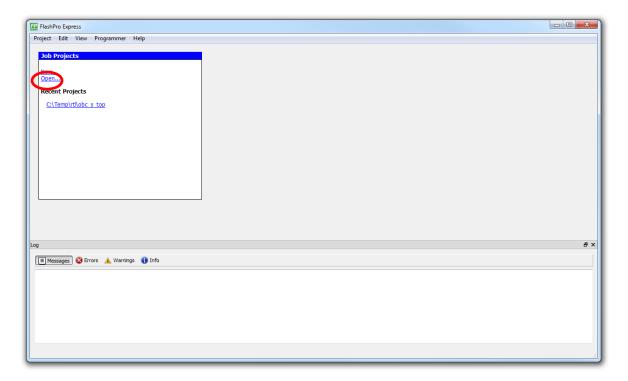

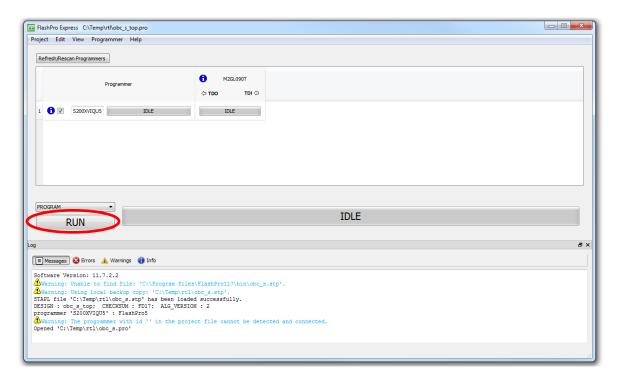

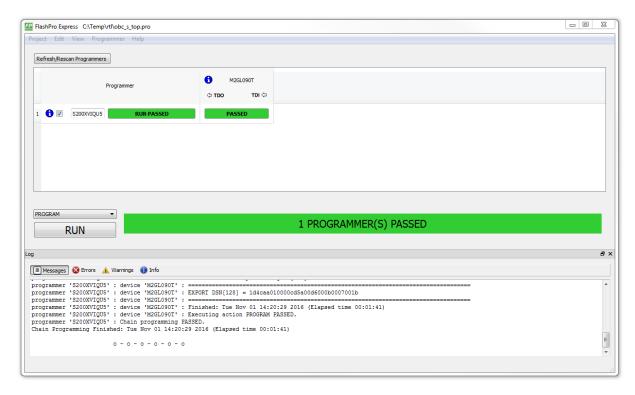

- Microsemi FlashPro Express v11.7, <a href="http://www.microsemi.com/products/fpga-soc/design-resources/programming/flashpro#software">http://www.microsemi.com/products/fpga-soc/design-resources/programming/flashpro#software</a>

- FlashPro5 programmer

# 3.2. Connecting cables to the Sirius products

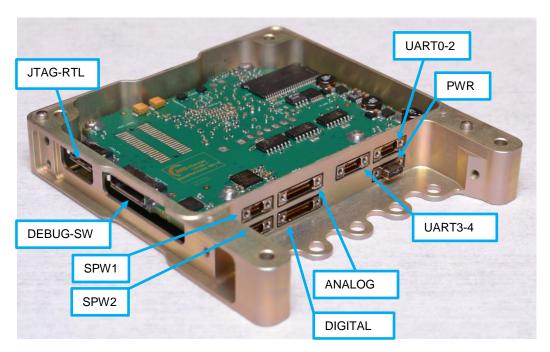

Figure 3-1 - ÅAC Sirius OBC with connector naming

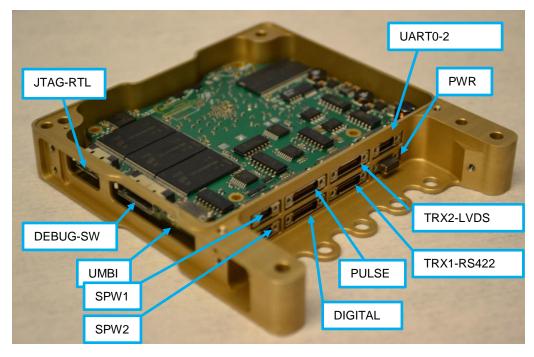

Figure 3-2 - ÅAC Sirius TCM with connector naming

The instructions below refer to the connector names in Figure 3-1 and Figure 3-2.

- All products and ingoing material shall be handled with care to prevent damage of any kind.

- ESD protection and other protective measures shall be considered. Handling should be performed according to applicable ESD requirement standards such as [RD12] or equivalent.

- Ensure that all mating connectors have the same zero reference (ground) before connecting.

- Connect the nano-D connector to the PWR connector with 4.5 16 V DC. The units will nominally draw about 260-300 mA @5V DC.

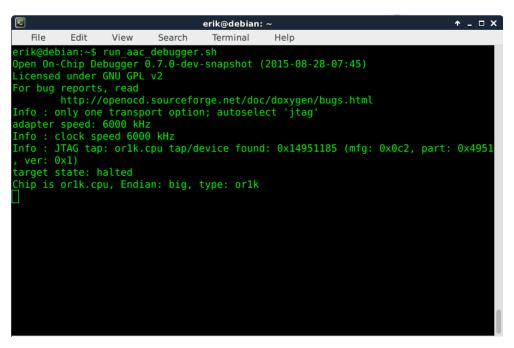

- The ÅAC debugger is mainly used for development of custom software for the Sirius OBC or Sirius TCM and has both a debug UART for monitoring and a JTAG interface for debug capabilities. It is also used for programming an image to the system flash memory. For further information refer to Chapter 3.6. When it is to be used, connect the 104452 ÅAC Debugger to the DEBUG-SW connector. Connect the adapter USB-connector to the host PC.